## CY25000

# Programmable Spread Spectrum Clock Generator for EMI Reduction

## Features

- Programmable spread spectrum with nominal 30-kHz modulation frequency

- Center spread: ±0.25% to ±2.5%

- Down spread: -0.5% to -5.0%

- Input frequency range

- External crystal: 8-30 MHz fundamental crystals

- External reference: 8–166 MHz Clock

- Integrated phase-locked loop (PLL)

- Programmable crystal load capacitor tuning array

- Low cycle-to-cycle Jitter

- 3.3V operation

- Spread spectrum On/Off function

- Power-down or Output Enable function

## **Benefits**

- Services most PC peripherals, networking, and consumer applications.

- Provides wide range of spread percentages for maximum EMI reduction, to meet regulatory agency Electro Magnetic Compliance (EMC) requirements. Reduces development and manufacturing costs and time-to-market.

- Eliminates the need for expensive and difficult to use higher order crystals.

- Internal PLL to generate up to 200-MHz output. Able to generate custom frequencies from an external crystal or a driven source.

- Enables fine-tuning of output clock frequency by adjusting  $\rm C_{Load}$  of the crystal. Eliminates the need for external  $\rm C_{Load}$  capacitors.

- Suitable for most PC, consumer, and networking applications

- Application compatibility in standard and low-power systems.

- Provides ability to enable or disable spread spectrum with an external pin.

- Enables low-power state or output clocks to High-Z state.

## **Pin Descriptions**

| Pin | Name      | Description                                                                                                                                                                                                                  |

|-----|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | XIN/CLKIN | Crystal input or reference clock input.                                                                                                                                                                                      |

| 2   | VDD       | 3.3V voltage supply.                                                                                                                                                                                                         |

| 3   | PD#/OE    | <b>Power-down pin</b> . Active LOW. If PD# = 0, SSCLK and REFCLK are three-stated.<br>Output Enable pin: Active HIGH. If OE = 1, SSCLK and REFCLK are enabled.<br>User has the option of choosing either PD# or OE function. |

| 4   | VSS       | GND.                                                                                                                                                                                                                         |

| 5   | SSCLK     | Spread spectrum clock output.                                                                                                                                                                                                |

| 6   | REFCLK    | Buffered reference output.                                                                                                                                                                                                   |

| 7   | SSON      | Spread spectrum control. 1 = Spread on. 0 = Spread off.                                                                                                                                                                      |

| 8   | XOUT      | Crystal output. Leave this pin floating if external clock is used.                                                                                                                                                           |

### **General Description**

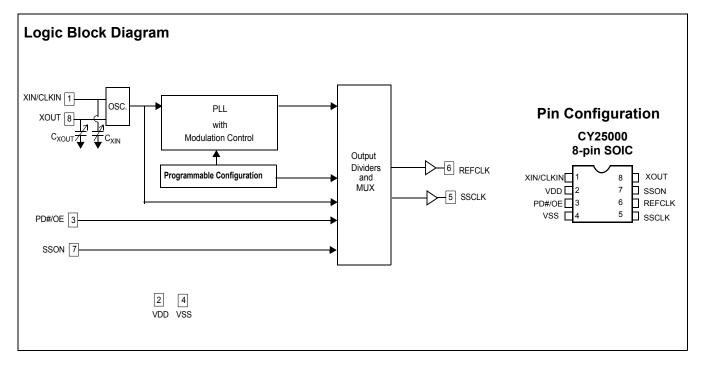

The CY25000 is a Spread Spectrum Clock Generator (SSCG) IC used for the purpose of reducing Electro Magnetic Interference (EMI) found in today's high-speed digital electronic systems.

The device uses a Cypress-proprietary PLL and Spread Spectrum Clock (SSC) technology to synthesize and modulate the frequency of the input clock. By frequency modulating the clock, the measured EMI at the fundamental and harmonic frequencies are greatly reduced. This reduction in radiated energy can significantly reduce the cost of complying with regulatory agency requirements (EMC) and improve time to market without degrading system performance.

The CY25000 uses a factory-programmable configuration memory array to synthesize output frequency, spread %, crystal load capacitor, reference clock on/off and PD#/OE options.

The spread % is factory programmed to either center spread or down spread with various spread percentages. The range for center spread is from  $\pm 0.25\%$  to  $\pm 2.50\%$ . The range for down spread is from -0.5% to -5.0%. Contact the factory for smaller or larger spread % amounts if required.

The input to the CY25000 can be either a crystal or a clock signal. The input frequency range for crystals is 8-30 MHz, and for clock signals is 8-166 MHz.

The CY25000 has two clock outputs, REFCLK and SSCLK. The non-spread spectrum REFCLK output has the same frequency as the input of the CY25000. The frequency modulated SSCLK output can be programmed from 3–200 MHz.

The CY25000 products are available in an 8-pin SOIC (150-mil) package with a commercial operating temperature range of 0 to  $70^{\circ}$ C.

## CY25000

## Absolute Maximum Rating

| Supply Voltage (V <sub>DD</sub> )–0.5 to +7.0V      |  |

|-----------------------------------------------------|--|

| DC Input Voltage –0.5V to $V_{\text{DD}}$ + 0.5     |  |

| Storage Temperature (Non-Condensing)–55°C to +125°C |  |

## **Operating Conditions**

| Junction Temperature                                       | –40°C to +125°C |

|------------------------------------------------------------|-----------------|

| Data Retention @ Tj=125°C                                  | > 10 Years      |

| Package Power Dissipation                                  | 350 mW          |

| Static Discharge Voltage<br>(per MIL-STD-883, Method 3015) | <u>≥</u> 2000V  |

| Parameter           | Description                                                                                   | Min. | Тур. | Max. | Unit |

|---------------------|-----------------------------------------------------------------------------------------------|------|------|------|------|

| V <sub>DD</sub>     | Supply Voltage                                                                                | 3.13 | 3.30 | 3.45 | V    |

| T <sub>A</sub>      | Ambient Temperature                                                                           | 0    |      | 70   | °C   |

| C <sub>LOAD</sub>   | Max. Load Capacitance @ pin 5 and pin 6                                                       |      |      | 15   | pF   |

| F <sub>ref</sub>    | External Reference Crystal<br>(Fundamental tuned crystals only)                               | 8    |      | 30   | MHz  |

|                     | External Reference Clock                                                                      | 8    |      | 166  | MHz  |

| F <sub>SSCLK</sub>  | SSCLK output frequency, C <sub>LOAD</sub> = 15 pF                                             | 3    |      | 200  | MHz  |

| F <sub>REFCLK</sub> | REFCLK output frequency, C <sub>LOAD</sub> = 15 pF                                            | 8    |      | 166  | MHz  |

| t <sub>PU</sub>     | Power-up time for all VDDs to reach minimum specified voltage (power ramps must be monotonic) | 0.05 |      | 500  | ms   |

## **DC Electrical Characteristics**

| Parameter                                             | Description                                | Condition                                                                                                                                | Min.               | Тур. | Max.        | Unit |

|-------------------------------------------------------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------|-------------|------|

| I <sub>ОН</sub>                                       | Output High Current                        | $V_{OH} = V_{DD} - 0.5$ , $V_{DD} = 3.3V$ (source)                                                                                       | 10                 | 14   |             | mA   |

| I <sub>OL</sub>                                       | Output Low Current                         | V <sub>OL</sub> = 0.5, V <sub>DD</sub> = 3.3V (sink)                                                                                     | 10                 | 14   |             | mA   |

| V <sub>IH</sub>                                       | Input High Voltage                         | CMOS levels, 70% of V <sub>DD</sub>                                                                                                      | 0.7V <sub>DD</sub> |      |             | V    |

| V <sub>IL</sub>                                       | Input Low Voltage                          | CMOS levels, 30% of V <sub>DD</sub>                                                                                                      |                    |      | $0.3V_{DD}$ | V    |

| IIH                                                   | Input High Current, PD#/OE and SSON pins   | V <sub>in</sub> = V <sub>DD</sub>                                                                                                        |                    |      | 10          | μA   |

| IIL                                                   | Input Low Current, PD#/OE<br>and SSON pins | V <sub>in</sub> = V <sub>SS</sub>                                                                                                        |                    |      | 10          | μA   |

| I <sub>OZ</sub>                                       | Output Leakage Current                     | Three-state output, PD#/OE = 0                                                                                                           | -10                |      | 10          | μA   |

| C <sub>XIN</sub> /C <sub>XOUT</sub> <sup>[1, 2]</sup> | Programmable Capacitance                   | Capacitance at minimum setting                                                                                                           |                    | 12   |             | pF   |

|                                                       | at pin 1 and pin 8                         | Capacitance at maximum setting                                                                                                           |                    | 60   |             | pF   |

| C <sub>IN</sub> <sup>[1]</sup>                        | Input Capacitance at pin 3 and pin 7       | Input pins excluding XIN and XOUT                                                                                                        |                    | 5    | 7           | pF   |

| I <sub>VDD</sub>                                      | Supply Current                             | V <sub>DD</sub> = 3.45V, Fin = 30 MHz,<br>REFCLK = 30 MHz, SSCLK = 66 MHz,<br>C <sub>LOAD</sub> = 15 pF, PD#/OE = SSON = V <sub>DD</sub> |                    | 25   | 35          | mA   |

| I <sub>DDS</sub>                                      | Stand by current                           | V <sub>DD</sub> = 3.45V, Device powered down with<br>PD#/OE = 0V                                                                         |                    | 15   | 30          | μA   |

## AC Electrical Characteristics<sup>[1]</sup>

| Parameter | Description            | Condition                                                                         | Min. | Тур. | Max. | Unit |

|-----------|------------------------|-----------------------------------------------------------------------------------|------|------|------|------|

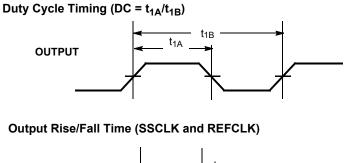

| DC        | Output Duty Cycle      | SSCLK, Measured at V <sub>DD</sub> /2                                             | 45   | 50   | 55   | %    |

|           | Output Duty Cycle      | REFCLK, Measured at V <sub>DD</sub> /2<br>Duty Cycle of CLKIN = 50%.              | 40   | 50   | 60   | %    |

| SR1       | Rising Edge Slew Rate  | SSCLK from 3 to 100 MHz; REFCLK from<br>10 to 100 MHz. 20%–80% of V <sub>DD</sub> | 0.7  | 1.1  | 1.5  | V/ns |

| SR2       | Falling Edge Slew Rate | SSCLK from 3 to 100 MHz; REFCLK from<br>10 to 100 MHz. 80%–20% of V <sub>DD</sub> | 0.7  | 1.1  | 1.5  | V/ns |

Notes:

Guaranteed by characterization, not 100% tested.

Contact factory for desired crystal load programming.

## AC Electrical Characteristics<sup>[1]</sup>

| Parameter        | Description                               | Condition                                                                           | Min. | Тур. | Max. | Unit |

|------------------|-------------------------------------------|-------------------------------------------------------------------------------------|------|------|------|------|

| SR3              | Rising Edge Slew Rate                     | SSCLK from 100 to 200 MHz; REFCLK<br>from 100 to 166 MHz 20%–80% of V <sub>DD</sub> | 1.2  | 1.6  | 2.0  | V/ns |

| SR4              | Falling Edge Slew Rate                    | SSCLK from 100 to 200 MHz; REFCLK<br>from 100 to 166 MHz 80%–20% of V <sub>DD</sub> | 1.2  | 1.6  | 2.0  | V/ns |

| tj1              | Peak Cycle-to-Cycle Jitter.               | SSCLK = 200 MHz. Spread on                                                          |      | 100  | 200  | ps   |

|                  | SSCLK pin                                 | SSCLK = 66 MHz. Spread on                                                           |      | 150  | 300  | ps   |

|                  |                                           | SSCLK = 14.3 MHz. Spread on                                                         |      | 200  | 400  | ps   |

| tj2              | Peak Cycle-to-Cycle Jitter,<br>REFCLK     | REFCLK output only                                                                  |      | 100  | 200  | ps   |

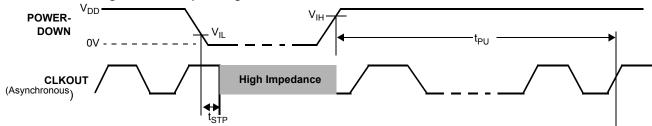

| t <sub>STP</sub> | Power-down Time<br>(pin3 = PD#)           | Time from falling edge on PD# to stopped outputs (Asynchronous)                     |      | 150  | 300  | ns   |

| T <sub>OE1</sub> | Output Disable Time<br>(pin3 = OE)        | Time from falling edge on OE to stopped outputs (Asynchronous)                      |      | 150  | 300  | ns   |

| T <sub>OE2</sub> | Output Enable Time<br>(pin3 = OE)         | Time from rising edge on OE to outputs at a valid frequency (Asynchronous)          |      | 150  | 300  | ns   |

| t <sub>PU1</sub> | Power-up Time,<br>Crystal is used         | Time from rising edge on PD# to outputs at valid frequency (Asynchronous)           |      | 3    | 5    | ms   |

| t <sub>PU2</sub> | Power-up Time,<br>Reference clock is used | Time from rising edge on PD# to outputs at valid frequency (Asynchronous)           |      | 2    | 3    | ms   |

#### Table 1.

| Pin<br>Function  | Input<br>Frequency | C <sub>XIN</sub> and<br>C <sub>XOUT</sub> | Output<br>Frequency | Spread<br>Percent | Reference<br>Output | Power-down or<br>Output Enable | Frequency<br>Modulation |

|------------------|--------------------|-------------------------------------------|---------------------|-------------------|---------------------|--------------------------------|-------------------------|

| Pin Name         | XIN and XOUT       | XIN and<br>XOUT                           | SSCLK               | SSCLK             | REFOUT              | PD#/OE                         | SSCLK                   |

| Pin#             | 1 and 8            | 1 and 8                                   | 5                   | 5                 | 6                   | 3                              | 5                       |

| Units            | MHz                | pF                                        | MHz                 | %                 | On or Off           | Select PD# or OE               | kHz                     |

| PROGRAM<br>VALUE | ENTER DATA         | ENTER DATA                                | ENTER DATA          | ENTER<br>DATA     | ENTER DATA          | ENTER DATA                     | 30                      |

## **Programming Description**

The customers planning to use the CY25000 need to provide the programming information described as "ENTER DATA" in *Table 1* and should contact local Cypress Sales.

Additional information on the CY25000 can be obtained from the Cypress web site at www.cypress.com.

#### **Product Functions**

#### Input Frequency (XIN, pin 1 and XOUT pin 8)

The input to the CY25000 can be a crystal or a clock. The input frequency range for crystals is 8 to 30 MHz, and for clock signal is 8 to 166 MHz.

#### C<sub>XIN</sub> and C<sub>XOUT</sub> (pin 1 and pin 8)

The load capacitors at pin 1 ( $C_{XIN}$ ) and pin 8 ( $C_{XOUT}$ ) can be programmed from 12 pF to 60 pF with 0.5-pF increments. The programmed value of these on-chip crystal load capacitors are the same (XIN = XOUT = 12 to 60 pF).

The required values of  $\textbf{C}_{\textbf{XIN}}$  and  $\textbf{C}_{\textbf{XOUT}}$  can be calculated using the following formula:

$C_{XIN} = C_{XOUT} = 2C_L - C_P$

Where  $C_L$  is the crystal load capacitor as specified by the crystal manufacturer and  $C_P$  is the parasitic PCB capacitance.

For example, if a fundamental 16-MHz crystal with C<sub>L</sub> of 16 pF is used and C<sub>P</sub> is 2 pF, C<sub>XIN</sub> and C<sub>XOUT</sub> can be calculated as:  $C_{XIN} = C_{XOUT} = (2 \times 16) - 2 = 30 \text{ pF}.$

$O_{XIN} = O_{XOUI} = (2 \times 10) = 2 = 30 \text{ pr}$

If using a driven reference, set  $C_{XIN}$  and  $C_{XOUT}$  to the minimum value 12 pF.

#### Output Frequency, SSCLK Output (SSCLK, pin 5)

The modulated frequency at the SSCLK output is produced by synthesizing the input reference clock. The modulation can be stopped by SSON digital control input (SSON = LOW, no modulation). If modulation is stopped, the clock frequency is the nominal value of the synthesized frequency without modulation (spread % = 0). The range of synthesized clock is from 3–200 MHz.

#### Spread Percentage (SSCLK, pin 5)

The SSCLK frequency can be programmed at any percentage value from  $\pm 0.25\%$  to  $\pm 2.5\%$  for Center Spread and from -0.5% to -5.0% Down Spread.

#### **Reference Output (REFOUT, pin 6)**

The reference clock output has the same frequency and the same phase as the input clock. This output can be programmed to be enabled (clock on) or disabled (High-Z, clock off). If this output is not needed, it is recommended that users request the disabled (High-Z, Clock Off) option.

#### Frequency Modulation

The frequency modulation is programmed at 30 kHz for all SSCLK frequencies from 3 to 200 MHz. Contact the factory if a higher modulation frequency is required.

#### Power-down or Output Enable (PD# or OE, pin 3):

Users can select either PD# or OE function which are also factory programmable.

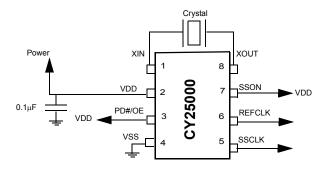

## **Application Circuit**<sup>[3, 4, 5]</sup>

#### **Switching Waveforms**

$\begin{array}{l} \mbox{Output Rise time (Tr) = (0.6 \ x \ V_{DD})/SR1 (or \ SR3) \\ \mbox{Output Fall time (Tf) = (0.6 \ x \ V_{DD})/SR2 (or \ SR4) \\ \mbox{Refer to AC Electrical Characteristics table for SR (Slew Rate) values.} \end{array}$

#### **Power-down Timing and Power-up Timing**

#### Notes:

- Since the load capacitors (C<sub>XIN</sub> and C<sub>XOUT</sub>) are provided by the CY25000, no external capacitors are needed on the XIN and XOUT pins to match the crystal load capacitor (C<sub>L</sub>). Only a single 0.1-µF bypass capacitor is required on the V<sub>DD</sub> pin.

- 4. If an external clock is used, apply the clock to XIN (pin 1) and leave XOUT (pin 8) floating (unconnected).

- 5. If SSON (pin 7) is LOW ( $V_{SS}$ ), the frequency modulation will be stopped on SSCLK pin (pin 5).

## Switching Waveforms (continued)

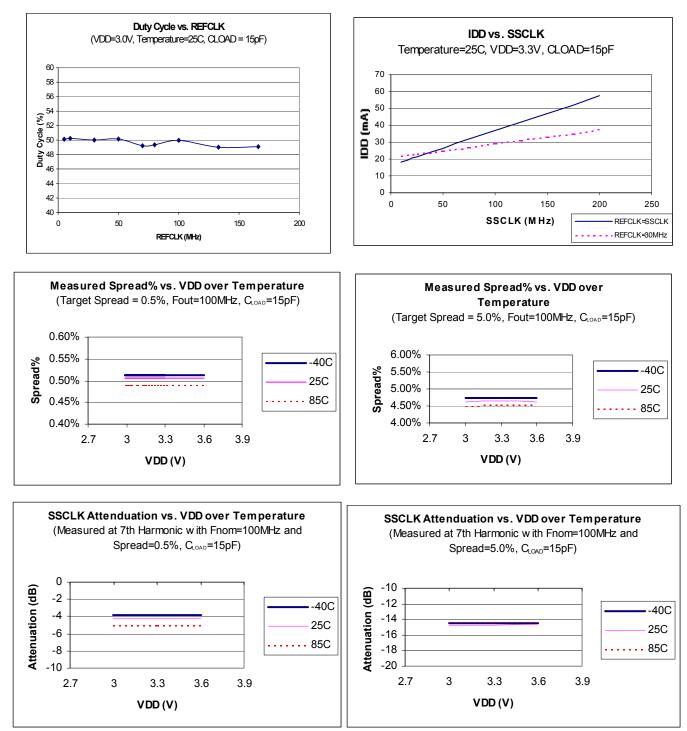

## **Informational Graphs**

## Informational Graphs (continued)

## Informational Graphs (continued)

## **Custom Configuration Request Procedure**

The CY25000 is a memory programmable device that is configured in the factory. All requests must be submitted to the local Cypress Field Application Engineer (FAE) or sales representative. A sample request form (refer to "CY25000 Sample

### Ordering Information

|                     | (8 |     |     | e-Cycle<br>Tem∣<br>MHz,V[ | peratu  | re |    |    |     |

|---------------------|----|-----|-----|---------------------------|---------|----|----|----|-----|

| _                   |    |     |     | 200                       |         |    |    |    |     |

| [S                  |    |     |     | 175                       |         |    |    |    | _   |

| 5                   |    |     |     | 150                       |         |    |    |    |     |

| te                  |    |     |     | 125                       |         |    |    |    | _   |

| Ē                   |    |     |     | 100                       |         |    |    |    | _   |

| ç                   |    |     |     | 75                        |         |    |    |    | _   |

| ů                   |    |     |     | 50                        |         |    |    |    |     |

| Maz C-C-jitter (ps) |    |     |     | 25                        |         |    |    |    |     |

| ~                   |    |     |     |                           |         |    |    |    |     |

| -6                  | 50 | -40 | -20 | 0                         | 20      | 40 | 60 | 80 | 100 |

|                     |    |     |     | Ten                       | np (deg | C) |    |    |     |

Request Form" at www.cypress.com) must be completed. Once the request has been processed, you will receive a new part number, samples and data sheet with the programmed values. This part number will be used for additional sample requests and production orders.

| Part Number <sup>[6]</sup> | Package Type                                                | Product Flow          |

|----------------------------|-------------------------------------------------------------|-----------------------|

| CY25XXXSC-W                | 8-pin Small Outline Integrated Circuit (SOIC)               | Commercial, 0 to 70°C |

| CY25XXXSC-WT               | 8-pin Small Outline Integrated Circuit (SOIC)–Tape and Reel | Commercial, 0 to 70°C |

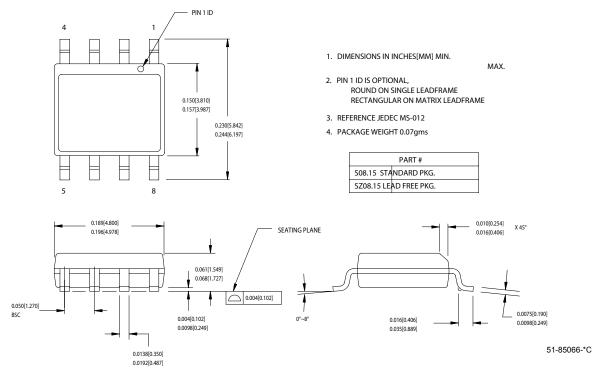

## **Package Drawing and Dimensions**

8-lead (150-Mil) SOIC S8

Note: 6. "XXX" denotes the assigned product number. "W" denotes the different programmed spread % values. The user can request different spread % values.

All product and company names mentioned in this document are the trademarks of their respective holders.

© Cypress Semiconductor Corporation, 2003. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress Semiconductor product. Nor does it convey or imply any license under patent or other rights. Cypress Semiconductor does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress Semiconductor products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress Semiconductor against all charges.

## **Document History Page**

| Document Title: CY25000 Programmable Spread Spectrum Clock Generator for EMI Reduction<br>Document Number: 38-07424 |         |            |                    |                                                                                                              |  |  |  |

|---------------------------------------------------------------------------------------------------------------------|---------|------------|--------------------|--------------------------------------------------------------------------------------------------------------|--|--|--|

| REV.                                                                                                                | ECN NO. | Issue Date | Orig. of<br>Change | Description of Change                                                                                        |  |  |  |

| **                                                                                                                  | 115076  | 06/20/02   | CKN                | New Data Sheet                                                                                               |  |  |  |

| *A                                                                                                                  | 121901  | 12/14/02   | RBI                | Power-up requirements added to Operating Conditions Information                                              |  |  |  |

| *В                                                                                                                  | 129855  | 10/01/03   | RGL                | Removed "PRELIMINARY" Changed $I_{OH}$ and $I_{OL}$ min. from 12 mA to 10 mA and typical from 24 mA to 14 mA |  |  |  |